条件に該当する製品156件

-

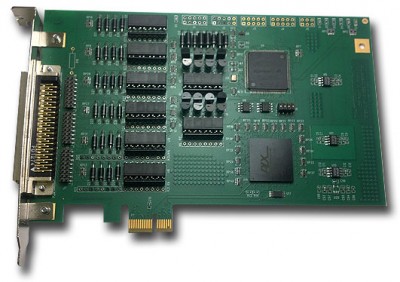

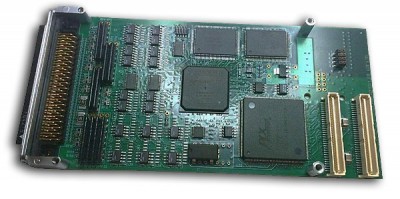

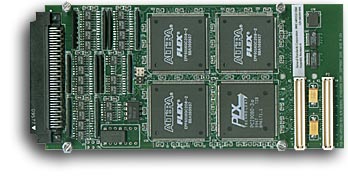

OPTO32C(Optically-Isolated I/O with Change-of-State Interrupts)

GneralStandardsCorporation デジタルI/O PMC/XMC 通信・ キャリアThe PCIe-OPTO32C board has 32 optically-coupled digital I/O channels consisting of 8 outputs and 24 inputs. Each channel is electrically isolated (1000 Volts) from the PMC host processor board. Change-of-State Interrupts allow for an interrupt to the PCI host to be generated from any level change on any input. Built-in-self-test, selectable debounce times, input pulse counter, and I/ O voltages to 50 Volts makes for a versatile digital interface board.

-

HVDO16MI (16-Channel, Isolated Digital Output Module With 16 Mutually Isolated High-Voltage High-Current Drivers)

GneralStandardsCorporation デジタルI/O CompactPCI 鉄道/交通16 Mutually Isolated open-collector digital output channels. Maximum load current: 1.2 Amp Voltage tolerance: Zero to +150V Isolation; Channel-to-Channel: Sustained 1000VRMS Isolation; Channel-to-Bus: Sustained 1000VRMS Zero-state: Switch closed; High state: Switch open Clamp diode protection Clocking: Static outputs; Register-controlled, one bit per channel. cPCI 6U form factor. Conformal coating ensures long-term insulation integrity. Front-Panel system I/O connections 66MHz 64-bit PCI support, with universal 5V/3.3V signaling and DMA support. PCI burst rates to 400MB/sec.

-

HVDI32MI-A(32 Galvanically-Isolated Digital Input Channels with Built-in Selftest (BIST) and dual thresholds)

GneralStandardsCorporation デジタルI/O CompactPCI 防衛32 galvanically isolated digital inputs Built-in selftest provides two detection thresholds for each channel, with three detection states of "Below Low threshold", "Above High threshold", or "Between thresholds" (Fault) Isolation Voltage: 1000VRMS; channel-to-channel and channel-to-bus Threshold adjustment range of 0.1V to +60V in increments of 0.02V; specified with order Minimum loading; less than 0.5mA Fast response, typically 2us, with selectable debounce times 66MHz 64-bit PCI support, with universal 5V/3.3V signaling Software Programmable clock debounce rate Software Programmable Change of State detection. Rising edge or falling edge per input channel. Software Programmable Interrupts on any or all Change of State bit(s) Software Pre-loadable Event counter on Input Bit 31 Programmable Interrupt on event counter overflow Programmable Little Endian / Big Endian swapping PCI cycles Asynchronous to local bus cycles Software Controlled Test LED True 6U CPCI form factor

-

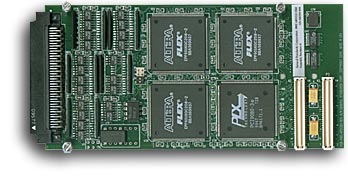

HPDI40C2L( High-speed 40-Bit Parallel Digital I/O PCI Board)

GneralStandardsCorporation デジタルI/O PMC/XMC 試験 環境600 Mbytes per second I/O transfer rate via the front panel connector (LVDS transceivers). 400 Mbytes per second PCI burst transfer rate over 300 Mbs sustained Upgrade in future to 600 MBps sustained Can interface to a wide variety of external high-speed devices. "Deep FIFO buffers" (4 Megabytes) allow data bursts to be transferred over the PCI bus. 64-Bit data transfers on the PCI bus. On-board cable controller, FIFOs, and DMA engine provide for continuous data transfer. Data input/output clock rate up to 150 MHz. 64-Bit, 66 MHz PCI v2.2 compliant Cable data input/output width of 32 bits. 8 bi-directional signals can be used as clocks and/or handshaking protocol.

-

HPDI32CL ( High-Speed 32-Bit Parallel Data Interface Board Up to 500 MByte/sec LVDS interface)

GneralStandardsCorporation デジタルI/O PCI Express 試験 環境Four Lane PCI Express (PCIe4) Interface PCIe Data transfers to/from Memory Buffers at speeds approaching 800 MByte/sec Large 512 MByte (128M x 32) Transmit/Receive Memory Buffers 500 MByte/sec Transfers to/from the Board via LVDS Front Panel Interface Bidirectional LVDS Transceivers provide for Multipoint Applications Half Duplex Operation - Transmit or Receive Mode Programmable Transmit Clock from 125MHz down to 50Hz Programmable Polarity for Clock and Data Valid Signals Five General Purpose IO Signals, including Interrupt Inputs Optional Receive Ready Signal for Data Throttling Interrupts available including DMA Completion, Transfer Status, Cable Status 80 pin Front Edge I/O Connector Standard Twisted Pair Ribbon Cables and Custom Cables available Windows and Linux drivers Available

-

HPDI32B-COS( 32 Bit Change of State Board With RS422/RS485 Transceivers)

GneralStandardsCorporation デジタルI/O PMC/XMC 鉄道/交通The PMC-HPDI32B-COS is a 32-bit parallel Change of State Detection board featuring high speed RS485 interface transceivers. The Change of State detection is can be customized to ignore specific bits and to provide an interrupt after a specified number of change of state events have occurred. The board will also function as a simple Logic Analyzer with a configurable trigger value and mask. The sample rate for both Change of State and Logic Analyzer is programmable from 20MHz down to 300Hz. Received values are buffered in an 8K deep on-board FIFO which is easily accessed by the integrated a DMA Controller. After the DMA is initialized and started, the host CPU will be free to proceed with other duties and need to respond only to interrupts. The DMA controller is capable of transferring data to host memory using D32 transfers; whereas the FIFO memory provides a means for continuous transmission of data without interrupting the DMA or requiring intervention from the host CPU.

-

HPDI32A(High-speed Digital I/O (Flexible Cable Interface))

GneralStandardsCorporation デジタルI/O PMC/XMC 鉄道/交通The PMC-HPDI32A board is a fast and flexible bi-directional 32-bit digital I/O board that transmits and receives data up to 80 Mbytes (differential I/O) or up to 200 Mbytes (Pseudo ECL I/O) per second. The board is useful as a general purpose DMA interface to a variety of external peripherals. The DMA engine is capable of transferring data to/from Host memory using D32 block transfers, while the FIFO memory (up to One Mbyte of total FIFO) provides continuous transmission of data without interrupting the DMA transfers or requiring intervention from the Host CPU. The board has 7 bi-directional programmable handshake lines and eight pre-configured software selectable interface protocols to allow easy interfacing to most digital I/ O peripherals. Available transceivers are RS485/422 and PECL. For TTL and LVDS transceiver versions, please see the PMC64-HPDI32ALT.

-

HPDI32A-DIPHASE(High-Speed Di-Phase Serial I/O (to 10Mbits/sec) with Deep FIFOs)

GneralStandardsCorporation シリアル PMC/XMC 通信・ キャリアThe PMC-HPDI32A-DIPHASE is a full-duplex RS-422/485 serial I/O board. Each channel can operate up to 10M bits/s. FIFO buffers up to 512K-byte for both transmit and receive (1M byte total) provides for a smooth and efficient interface between the serial interfaces and the host computer. The high-speed di-phase transmit/receive is implemented in an FPGA and provides for protocol flexibility. It features a full duplex DMA interface.

-

HPDI32A-COS( PMC Digital I/O with Change-of-State)

GneralStandardsCorporation デジタルI/O PMC/XMC 通信・ キャリアThe HPDI32A-COS board is a 32-Bit parallel digital input board that samples input data (via the cable interface) at selectable rates. The board can detect any Change-of-State and store the changed data word data in the on-board FIFO. The board is programmable and can generate an interrupt on the first detected change or upon any desired number of changes. Deep FIFO buffers (128 Kbytes) allow data bursts to be transferred over the PCI bus independent of transfers over the cable. Change-Of-State boards allow for more efficient monitoring of peripheral or industrial type devices (transducers, etc.). The board can also be used in a (logic analyzer) type mode by storing up to 64,000 samples after receipt of a trigger word. FIFOs, DMA engine, PCI controller, differential receivers, and multiple status interrupts provides high bandwidth along with complete board control.

-

HPDI32A-ASYNC( High-Speed Async Serial I/O (to 5Mbits/sec) with Deep FIFOs)

GneralStandardsCorporation シリアル PMC/XMC 通信・ キャリアThe PMC-HPDI32A-ASYNC is a full-duplex RS-422/485 serial I/O board. Each channel can operate up to 5M bits/ s. FIFO buffers up to 512K-byte for both transmit and receive (1M byte total) provides for a smooth and efficient interface between the serial interfaces and the host computer. The high speed async transmit/receive is implemented in an FPGA and provides for protocol flexibility. It features a full duplex DMA interface.